Đánh đổi thiết kế tương tự trong việc áp dụng kỹ thuật tuyến tính hóa sử dụng mạch CMOS mẫu

Bài viết này sẽ xem xét những đánh đổi mà chúng ta phải đối mặt khi cố gắng cải thiện độ tuyến tính của mạch.

Thiết kế mạch tích hợp kỹ thuật số thường liên quan đến việc tối ưu hóa ba thông số khác nhau: tốc độ, diện tích silicon bị chiếm dụng và điện năng tiêu thụ. Tuy nhiên, trong thiết kế tương tự, chúng ta phải xem xét một số khía cạnh khác của hiệu suất mạch như độ tuyến tính, tiếng ồn, trở kháng đầu vào / đầu ra, độ ổn định và dao động điện áp. Thường có sự đánh đổi giữa các thông số này và chúng tôi không thể cải thiện tất cả chúng đồng thời. Bài viết này sẽ xem xét những đánh đổi mà chúng ta phải đối mặt khi cố gắng cải thiện độ tuyến tính của mạch. Chúng ta sẽ thấy rằng độ tuyến tính của mạch thường giao dịch với độ lợi, độ ồn và tốc độ. Chúng ta sẽ kiểm tra các mạch tương tự CMOS đơn giản để có được trực giác về những đánh đổi này.

Nguồn gốc của sự không tuyến tính

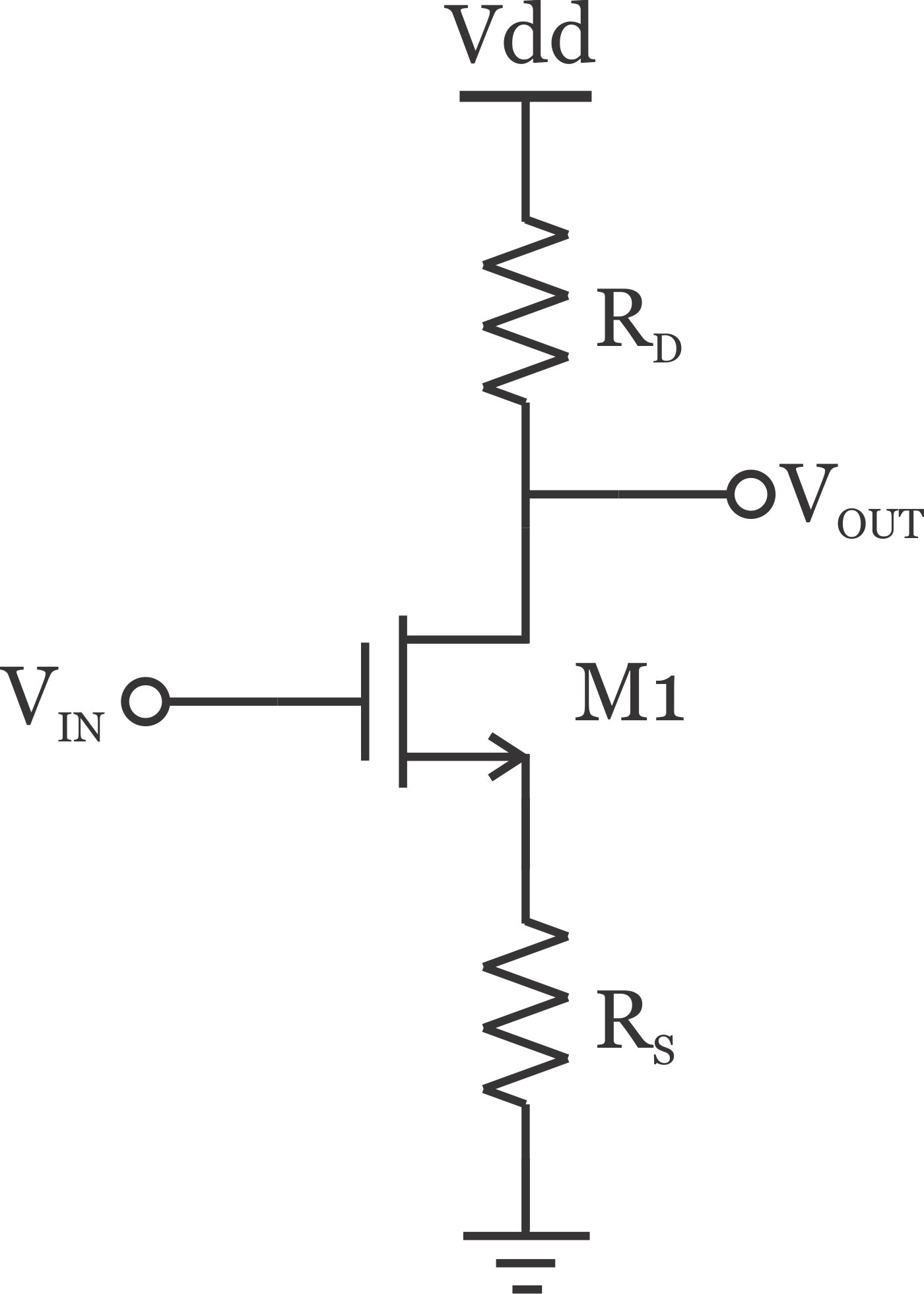

Hiệu suất tuyến tính xác định tín hiệu lớn nhất mà mạch có thể xử lý với độ chính xác chấp nhận được. Với tín hiệu đầu vào lớn, các thông số mạch có thể thay đổi đáng kể theo biên độ tức thời của đầu vào. Ví dụ, hãy xem xét bộ khuếch đại nguồn chung được hiển thị trong Hình 1.

Hình 1. Một mạch khuếch đại nguồn chung

Bỏ qua điện trở ra của tranzito, công suất điện áp của đoạn mạch này là Ở đâu biểu thị độ dẫn điện của transistor. Xem xét mô hình luật bình phương cho bóng bán dẫn MOS, chúng ta có:

trong đó k ' là tham số phụ thuộc vào quy trình vàchỉ định kích thước của bóng bán dẫn. Trong phương trình này, và tương ứng là điện áp nguồn cổng và điện áp ngưỡng của bóng bán dẫn. Phương trình trên cho thấy rằng, và do đó, độ lợi phụ thuộc vào điện áp nguồn cổng bóng bán dẫn. Với ví dụ được mô tả trong hình 1,thay đổi từ 0,5 V đến 1,5 V. Do đó, mạch sẽ thể hiện độ lợi cao hơn khi chúng ta tiếp cận đỉnh của đầu vào. (Chúng tôi giả định rằng đầu ra không bị bão hòa vì sự thay đổi điện áp có sẵn ở cống bóng bán dẫn. Với mức đủ lớn, giá trị DC của đầu ra sẽ gần với mặt đất và chúng ta sẽ có một dao động rất hạn chế ở đầu ra. Trong trường hợp này, lợi nhuận thực sự có thể giảm khi tăng). Sự thay đổi phụ thuộc vào đầu vào của độ lợi là nguồn gốc của sự không tuyến tính của mạch. Lưu ý rằng, khi chúng ta tăng biên độ của đầu vào, mạch ngày càng trở nên phi tuyến tính. Chúng ta đã thảo luận trong một bài viết trước về SFDR rằng sự không tuyến tính của mạch có thể dẫn đến một số thành phần tần số khác nhau ở đầu ra ngay cả khi đầu vào là hình sin đơn âm. Bây giờ, chúng ta hãy xem xét những đánh đổi phổ biến mà chúng ta phải đối mặt khi cố gắng cải thiện độ tuyến tính của mạch.

Đánh đổi tốc độ và tuyến tính

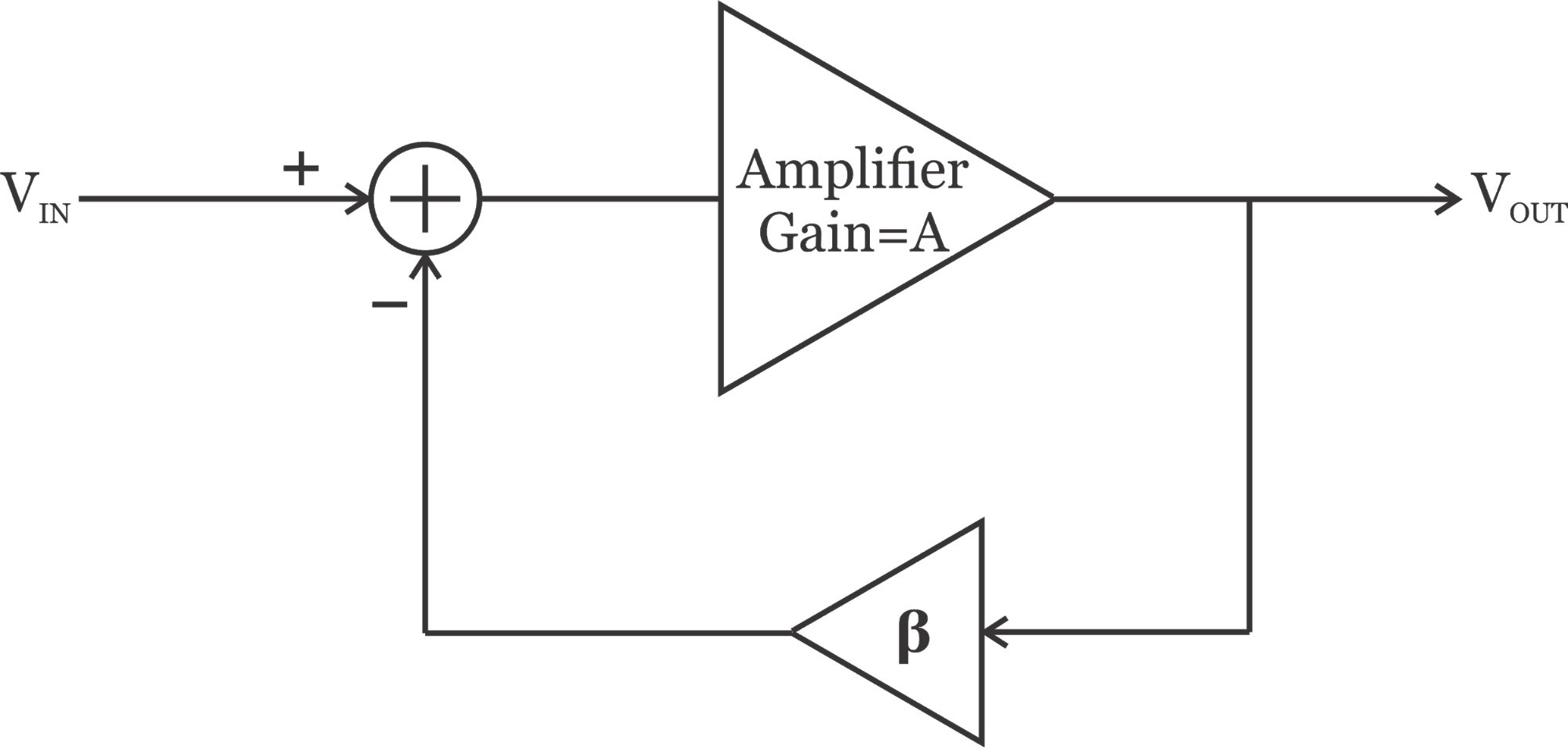

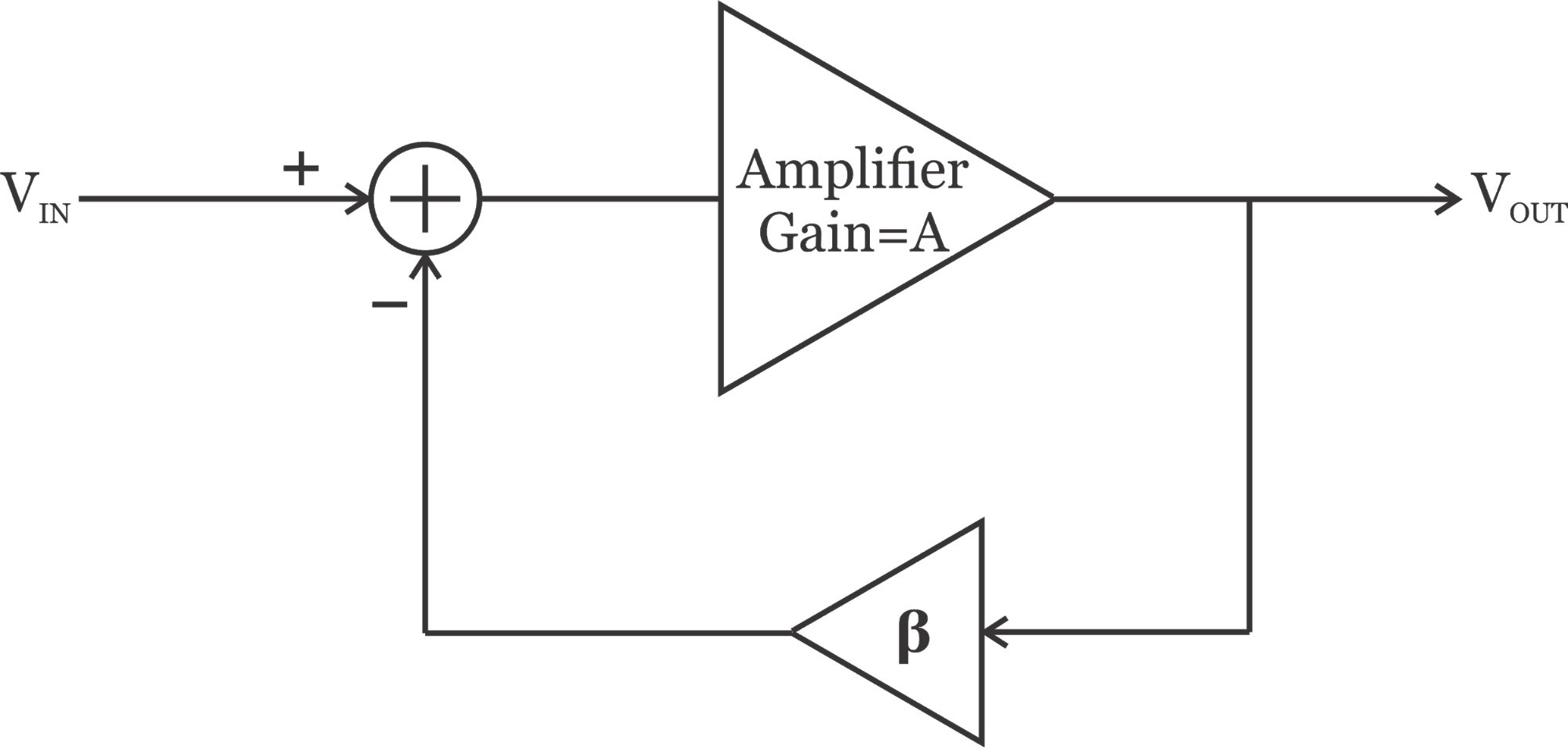

Một phương pháp phổ biến để tuyến tính hóa một mạch là kỹ thuật hồi tiếp âm được minh họa trong Hình 2.

Hình 2. Kỹ thuật hồi tiếp âm của tuyến tính hóa mạch.

Độ lợi vòng kín của mạch này được cho bởi:

Phương trình 1

Giả sử rằng , chúng ta có

Bộ khuếch đại nguồn cấp dữ liệu được thực hiện bằng cách sử dụng bóng bán dẫn và có thể có hành vi phụ thuộc vào đầu vào tương tự như bộ khuếch đại một tầng được thảo luận trong phần trước. Nói cách khác, giá trị của A có thể thay đổi đáng kể với biên độ đầu vào. Tuy nhiên, đường dẫn phản hồi thường được thực hiện bằng cách sử dụng các phần tử thụ động như điện trở và tụ điện. Các phần tử thụ động tuyến tính hơn nhiều so với các phần tử hoạt động và chúng ta có thể giả định rằngkhông phụ thuộc vào biên độ đầu vào. Nếu không áp dụng kỹ thuật phản hồi tiêu cực, độ lợi ( A ) có thể thay đổi theo đầu vào và chúng ta sẽ có một hệ thống phi tuyến tính. Tuy nhiên, lợi ích vòng kín là không đổi (giả sử rằng ).

Chi phí của cải tiến này là bao nhiêu? Độ tuyến tính của mạch thường giao dịch với độ lợi, độ ồn, tốc độ và mức tiêu thụ điện năng. Một trong những sự đánh đổi quan trọng có thể quan sát được trong kỹ thuật tuyến tính hóa dựa trên phản hồi là sự đánh đổi tốc độ và tuyến tính. Hãy xem xét sự đánh đổi này chi tiết hơn. Với hệ thống vòng lặp mở, chúng ta không phải lo lắng về sự ổn định. Hệ thống có thể tạo ra một độ trễ từ đầu vào đến đầu ra và khi chúng ta tăng tần số đầu vào, độ trễ sẽ tăng lên. Tuy nhiên, sự chậm trễ được giới thiệu có lẽ sẽ không gây ra vấn đề nghiêm trọng. Đây không phải là trường hợp của một hệ thống vòng kín mà chúng ta phải xem xét cẩn thận độ trễ của vòng lặp bởi vì sự dịch pha đủ lớn có thể làm cho phản hồi tích cực một cách hiệu quả. Thông thường, việc tăng tần số đầu vào của bộ khuếch đại làm giảm độ lợi và tăng độ lệch pha của nó.và độ lợi của vòng lặp vẫn có thể lớn hơn , dẫn đến bất ổn. (Xem bài viết của AAC về tính ổn định của phản hồi tiêu cực để biết thêm thông tin.)

Để làm cho hệ thống vòng kín ổn định, chúng ta phải áp dụng các kỹ thuật bù tần số để giảm đủ độ lợi vòng lặp xuống dưới 1 khi chuyển pha vòng lặp là 180 °. Về mặt khái niệm, điều này tương đương với việc đặt một bộ lọc thông thấp trong vòng lặp. Các bộ lọc thông thấp triệt tiêu tín hiệu tần số cao, do đó, chúng tôi hy vọng tần số hoạt động của hệ thống vòng kín sẽ bị hạn chế hơn nhiều so với tần số của bộ khuếch đại không bù ban đầu. Tóm lại, áp dụng phản hồi tiêu cực làm tăng tính tuyến tính với chi phí giảm tần suất hoạt động.

Sự cân bằng giữa lợi ích và tuyến tính

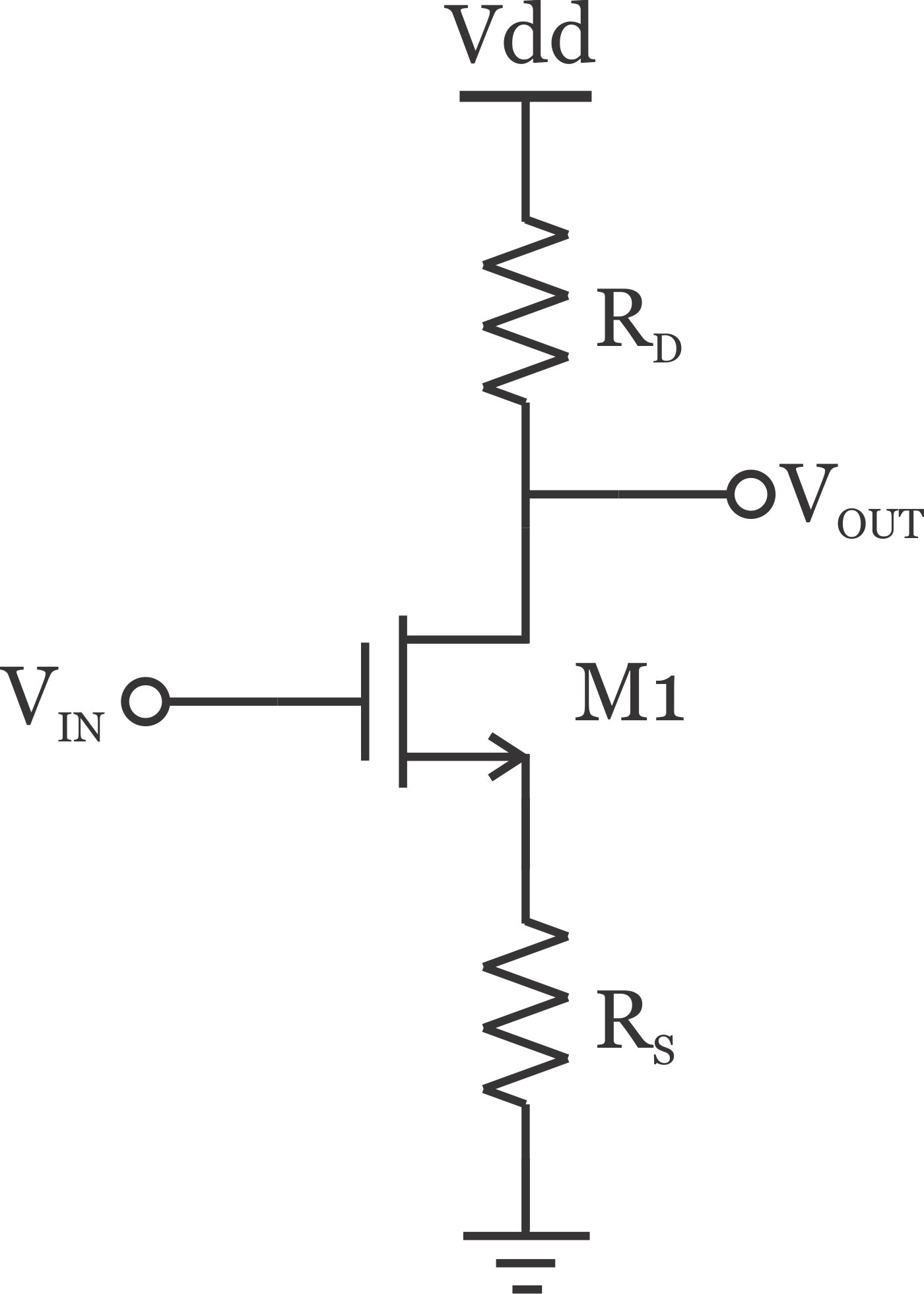

Một kỹ thuật tuyến tính hóa cơ bản là thoái hóa nguồn. Như được mô tả trong Hình 3, kỹ thuật này đặt một điện trở tuyến tínhở nguồn của bóng bán dẫn. Lưu ý rằng chúng ta có thể coi mạch này như một cấu trúc với “phản hồi cục bộ” lấy mẫu dòng xả và cấp lại một điện áp tỷ lệ mắc nối tiếp với điện áp đầu vào. Do đó, không có gì ngạc nhiên khi sự suy giảm nguồn làm tăng độ tuyến tính của mạch.

Hình 3. Thoái hóa nguồn được sử dụng như một kỹ thuật tuyến tính hóa cơ bản.

Bỏ qua điện trở đầu ra của bóng bán dẫn, độ tự cảm của mạch này là:

Phương trình 2

Giả sử rằng , chúng ta có , không phụ thuộc vào biên độ đầu vào. Việc cải thiện độ tuyến tính này đạt được với chi phí là giảm độ lợi. Không có điện trở thoái hóa, chúng tôi sẽ có một chất dẫn điện của . Nếu chúng ta thêm điện trở suy giảm, mạch trở nên tuyến tính; tuy nhiên, độ dẫn tổng thể bị giảm xuống giá trị được cho bởi Công thức 2. (Lưu ý rằng mẫu số của phương trình này được giả định là lớn hơn nhiều, do đó, độ dẫn điện bị giảm.) Do đó, có thể có sự cân bằng giữa độ lợi và tuyến tính.

Đánh đổi độ ồn và độ tuyến tính

Độ tuyến tính của mạch cũng có thể đánh đổi với hiệu suất nhiễu của nó. Điều này có thể được hiểu một cách đơn giản bằng cách lưu ý thực tế là chúng ta phải tăng độ phức tạp của mạch để làm cho nó tuyến tính hơn. Các yếu tố được thêm vào sẽ góp phần vào tiếng ồn tổng thể của mạch. Ví dụ, điện trở suy giảm trong Hình 3 sẽ hoạt động như một nguồn nhiễu bổ sung.

Phần kết luận

Trong thiết kế tương tự, chúng ta phải xem xét một số khía cạnh của hiệu suất mạch như tốc độ, công suất tiêu thụ, độ tuyến tính, tiếng ồn, trở kháng đầu vào / đầu ra, độ ổn định và sự thay đổi điện áp. Thường có sự đánh đổi giữa các thông số này và chúng tôi không thể cải thiện tất cả chúng đồng thời. Trong bài viết này, chúng ta đã thảo luận về những đánh đổi phổ biến mà chúng ta phải đối mặt khi cố gắng cải thiện độ tuyến tính của mạch. Chúng tôi thấy rằng tuyến tính của mạch thường giao dịch với các thông số như độ lợi, tiếng ồn và tốc độ.

Không có nhận xét nào