Khi định luật Moore kết thúc, Samsung phát hành công nghệ vi mạch 3D

Samsung đã công bố sự sẵn có của công nghệ vi mạch 3D của mình ở cả 7nm và 5nm. Công nghệ này giúp gì cho các nhà thiết kế hệ thống?

Samsung đã gây chú ý vào tuần trước khi công bố sự sẵn có của công nghệ vi mạch 3D mới nhất của mình .

Công nghệ mới, được gọi là X-Cube, đã được thử nghiệm và chứng minh trong một chip thử nghiệm 7nm, xếp chồng SRAM lên trên một chip logic. Kết quả là dấu chân nhỏ hơn và đường dẫn tín hiệu ngắn hơn, có nghĩa là tín hiệu truyền nhanh hơn và tiêu thụ ít điện năng hơn. X-Cube cũng có sẵn trong các nút nâng cao: cả 7nm và 5nm.

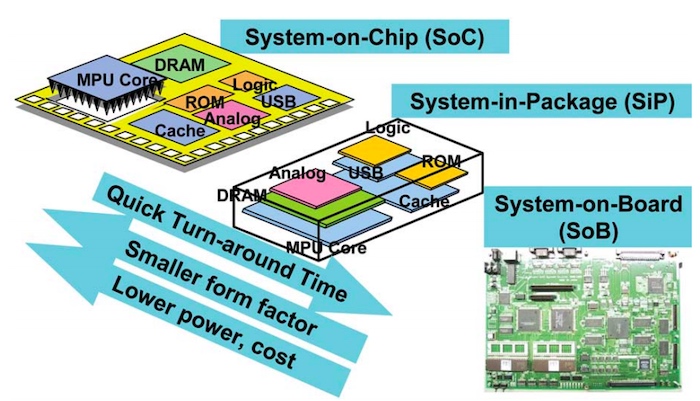

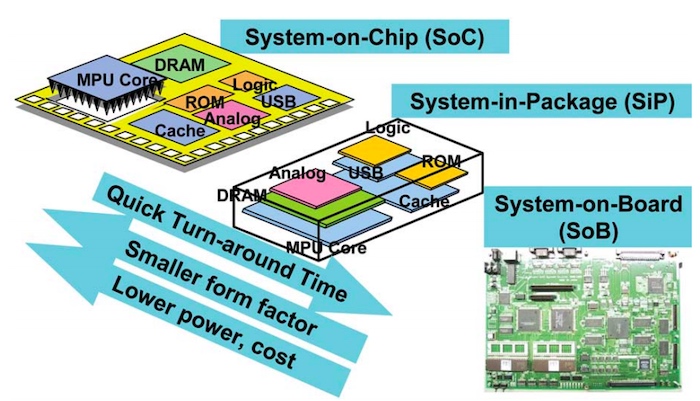

So sánh trong SoC, SiP và SoB. Hình ảnh được sử dụng với sự cho phép của Resve Salah et al.

Tiến bộ này của Samsung giải quyết một số xu hướng trong thiết kế chip: đối mặt với sự kết thúc của định luật Moore, tăng chức năng chip và giải quyết những khó khăn của hệ thống trên chip (SoC).

Vấn đề với việc tăng kích thước SoC

Một trong những thách thức lớn trong thiết kế SoC là việc tích hợp nhiều khối chức năng hơn vào một chip đòi hỏi diện tích chip lớn hơn đáng kể .

Nhưng sự kết hợp của diện tích chip lớn hơn và kích thước nút nhỏ hơn sau đó dẫn đến sự gia tăng lớn về ký sinh trùng liên kết. Chiều dài dây dài hơn phải được sử dụng để kết nối các khối khác nhau trong một chip vật lý lớn hơn, điều này làm tăng độ tự cảm kết nối.

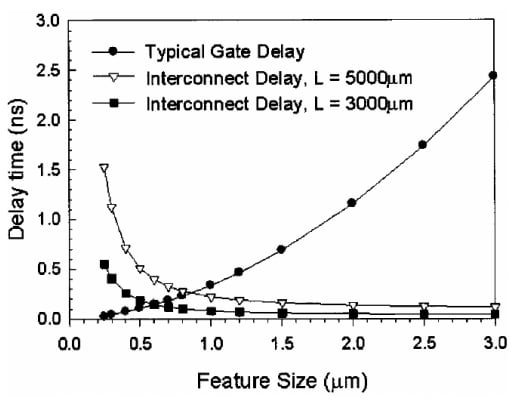

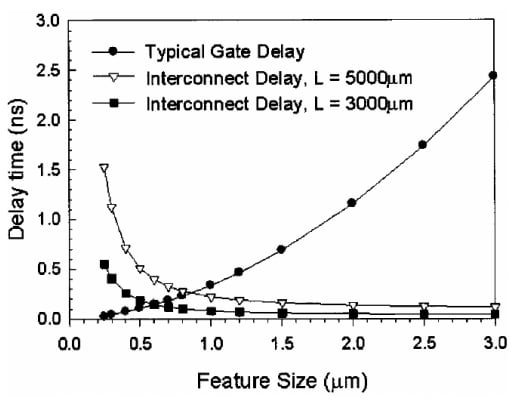

Nguồn của độ trễ dựa trên kích thước tính năng và độ dài kết nối. Hình ảnh được sử dụng bởi Parag Gadarki

Trở kháng ký sinh gia tăng của các kết nối đã kéo theo một loạt các vấn đề. Năng lượng di chuyển dữ liệu — năng lượng tiêu thụ từ chuyển động vật lý của dữ liệu trên chip — trở thành một trong những nguồn tiêu thụ năng lượng lớn nhất.

Độ trễ lan truyền tín hiệu cũng bị ảnh hưởng tiêu cực bởi chiều dài dây tăng lên và các kết nối ký sinh. Tuy nhiên, khi định luật Moore kết thúc, các nhà thiết kế phải nghĩ ra những cách mới để tăng tốc độ chip mà không phải thu nhỏ theo cách thông thường.

Giải pháp: IC 3D

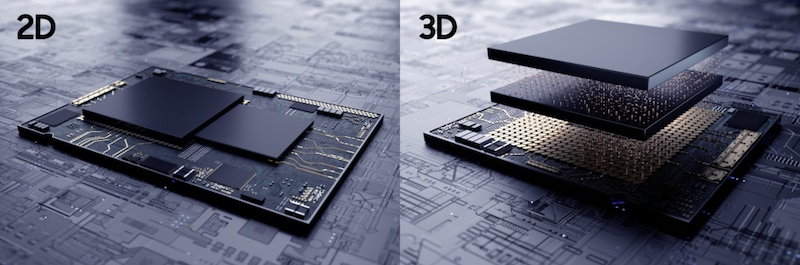

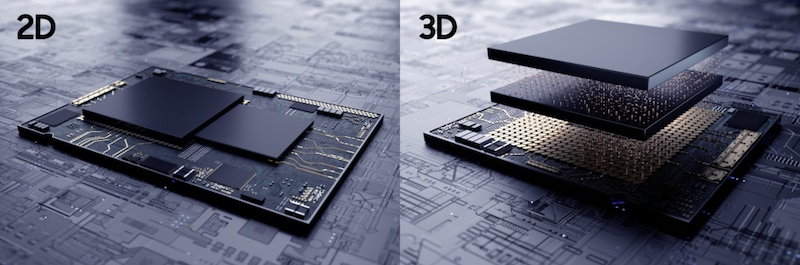

Để cho phép các chip liên tục mở rộng về kích thước trong khi khắc phục những vấn đề nói trên, các nhà thiết kế đã chuyển sang công nghệ 3D IC. Các vi mạch 3D đặc biệt ở chỗ chúng có thể xếp chồng các tấm silicon hoặc khuôn lên trên nhau.

Minh họa công nghệ vi mạch 3D. Hình ảnh được sử dụng với sự hỗ trợ của Samsung

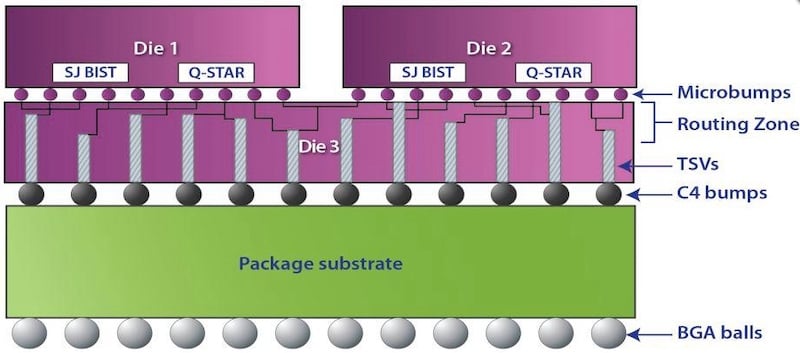

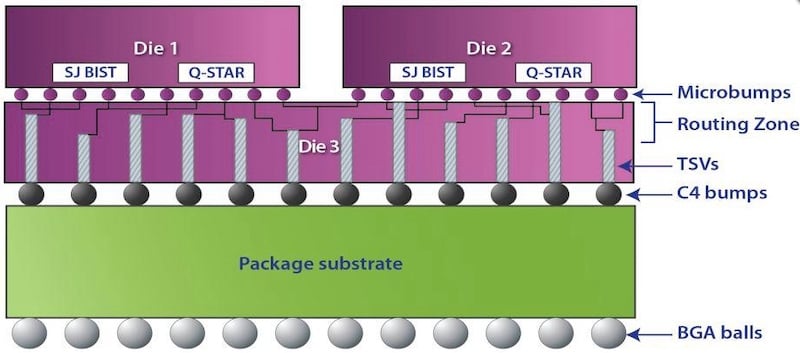

Mỗi tấm wafer trên một vi mạch 3D được kết nối với một silicon xuyên qua (TSV) . Bằng cách này, các con chip có thể tiếp tục phát triển về kích thước - nhưng thay vì dài hơn và rộng hơn trong 2D, chúng phát triển cao hơn trong 3D, tiết kiệm diện tích bảng.

Lợi ích của IC 3D

Các vi mạch 3D mang lại nhiều lợi ích hơn so với các SoC thông thường, diện tích lớn, hầu hết đều xuất phát từ việc rút ngắn kết nối. Với các khối chức năng được xếp chồng lên nhau và được kết nối thông qua TSV thay vì các dây dài như trong SoC 2D, các IC 3D có thể giảm đáng kể độ dài kết nối.

Đáng chú ý nhất, việc giảm độ dài kết nối giúp giảm bớt trở kháng ký sinh trong kết nối, do đó cho phép giảm độ trễ lan truyền (tức là hoạt động nhanh hơn) và ít năng lượng di chuyển dữ liệu hơn (tức là tiêu thụ ít điện năng hơn).

Công nghệ vi mạch 3D sử dụng TSV. Hình ảnh được sử dụng với sự hỗ trợ của Ridgetop Group

Lợi ích rõ ràng khác của IC 3D là khả năng tích hợp mật độ chức năng lớn vào các khu vực nhỏ hơn, cung cấp một giải pháp thay thế tốt cho sự kết thúc của định luật Moore. Cần lưu ý rằng sự tích hợp dày đặc này cũng đi kèm với những hạn chế như tăng mật độ điện năng và các vấn đề quản lý nhiệt.

Samsung giới thiệu công nghệ vi mạch 3D có thể tiếp cận

Tin tức của Samsung có thể đánh dấu sự khởi đầu của công nghệ vi mạch 3D tiên tiến và dễ tiếp cận. Moonsoo Kang, Phó chủ tịch cấp cao về chiến lược thị trường đúc tại Samsung Electronics cho biết, "Công nghệ tích hợp 3D mới của Samsung đảm bảo kết nối TSV đáng tin cậy ngay cả tại các nút quy trình EUV tiên tiến nhất."

Ông cho biết thêm, "Chúng tôi cam kết mang lại nhiều đổi mới vi mạch 3D có thể đẩy ranh giới của chất bán dẫn."

Trong tương lai, Samsung có kế hoạch xây dựng dựa trên thiết kế ban đầu, hợp tác với các khách hàng nổi tiếng toàn cầu để triển khai các giải pháp vi mạch 3D trong các ứng dụng hiệu suất cao thế hệ tiếp theo, như điện thoại thông minh di động, AR / VR, thiết bị đeo được và nền tảng máy tính hiệu suất cao.

Không có nhận xét nào