Thiết kế trình điều khiển I / O cho các mô-đun I2C mạch tích hợp

Bài viết này thảo luận về việc thiết kế trình điều khiển đầu vào / đầu ra cho mô-đun I2C mạch tích hợp.

I²C là một giao diện nối tiếp đồng bộ, đa chủ, đa phụ cho phép các vi mạch giao tiếp với nhau. Là một tiêu chuẩn giao tiếp mở / thu hở, I²C cho phép các mạch tích hợp (IC) giao tiếp ngay cả khi chúng sử dụng các đường ray điện áp khác nhau.

Bốn tốc độ của tiêu chuẩn I²C

Có bốn tốc độ hoạt động trong tiêu chuẩn I²C:

- Chế độ tiêu chuẩn: 100 kHz

- Chế độ nhanh: 400 kHz

- Chế độ nhanh cộng: 1 MHz

- Chế độ tốc độ cao: 3,4 MHz

Dòng xe buýt I²C: Dữ liệu nối tiếp và đồng hồ nối tiếp

Các xe buýt I ² C sử dụng hai dòng-sê-ri dữ liệu (SDA) và đồng hồ nối tiếp (SCL) -và tất cả các thiết bị chủ I ² C và nô lệ được nối với nhau bằng chỉ có hai dòng này. Mỗi thiết bị có thể vừa là máy phát vừa là máy thu.

Cả hai tín hiệu SDA và SCL là hai chiều. Các chân SDA và SCL của mỗi thiết bị là các chân thoát hở. Chúng có các điện trở kéo lên được kết nối với chúng để có được logic 1. Logic 1 phụ thuộc vào điện áp cung cấp; không có điện áp bus tiêu chuẩn.

Cấu trúc ô I²C

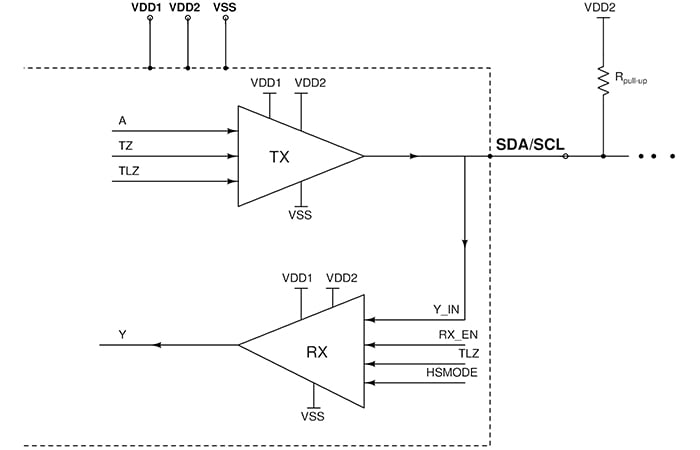

Hãy để chúng tôi thảo luận về cấu trúc ô I / O I²C được tích hợp trong vi mạch. Sơ đồ khối của cấu trúc ô I²C I / O được thể hiện trong Hình 1.

Hình 1. Sơ đồ khối của trình điều khiển I / O I²C

Khối TX được bật trong khung thời gian truyền trong khi khối RX được bật trong khung thời gian nhận.

VDD1 và VDD2 là hai đường dẫn điện áp khác nhau, nơi chủ và phụ hoạt động. VDD1 là nguồn cung cấp của chip cho các hoạt động bên trong và VDD2 là điện áp cung cấp mà hệ thống bên ngoài sử dụng. Để hỗ trợ các đường ray điện áp khác nhau, cần có một bộ dịch mức để dịch tín hiệu từ điện áp nguồn này sang điện áp cung cấp khác.

Mạch phát trong mô-đun I²C

Sơ đồ khối mạch máy phát được thể hiện trên hình 2.

Hình 2. Sơ đồ khối máy phát

A là tín hiệu dữ liệu được truyền ra trên chân SDA / SCL. TLZ là bộ điều khiển bộ ba trong khi ngắt nguồn VDD1. TZ được chuyển mức từ VDD1 sang VDD2 để kích hoạt bộ đệm thoát mở đầu ra cho A_OUT.

Nếu VDD1 bị tắt nguồn trong quá trình hoạt động của hệ thống do cố ý hoặc vô ý với VDD2 vẫn hoạt động, tín hiệu cho phép TZ ở mức thấp hoặc hầu như không được xác định. Điều này có thể kích hoạt bộ đệm đầu ra thành A_OUT.

Tín hiệu TLZ được sử dụng như một cơ chế an toàn khi thất bại. TLZ được kéo xuống trong quá trình sập nguồn, kéo tín hiệu TZ lên cao. Tại thời điểm này, bộ đệm đầu ra không được kích hoạt nữa. Bộ đệm thoát mở sẽ ở trong tình trạng ba lần khi VDD1 bị tắt nguồn.

Để tìm hiểu thêm về các trường hợp sử dụng, lợi ích và ứng dụng của việc sử dụng bộ đệm I²C, hãy xem bài viết kỹ thuật của AAC về thời điểm sử dụng bộ đệm I²C .

Mạch thu trong mô-đun I²C

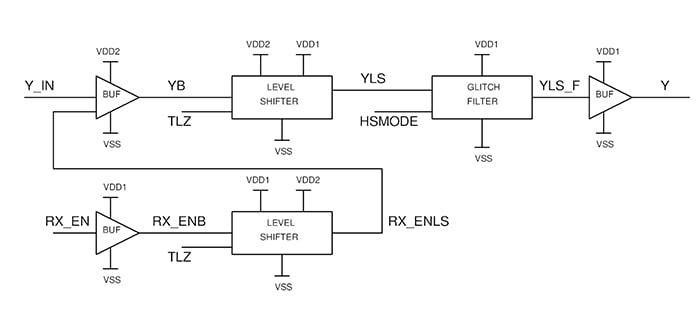

Sơ đồ khối mạch thu được thể hiện trong hình 3.

Hình 3. Sơ đồ khối máy thu

Mạch thu được kích hoạt với tín hiệu RX_EN. TLZ có chức năng tương tự như trong khối máy phát. Tín hiệu HSMODE bật chế độ tốc độ cao.

Tín hiệu RX_EN được chuyển mức từ VDD1 sang VDD2 để kích hoạt bộ đệm nhận tín hiệu Y_IN. Sau đó, một bộ dịch mức chuyển tín hiệu Y_IN được đệm đến thanh ray điện áp VDD1.

Sử dụng bộ lọc trục trặc

Tín hiệu I²C dễ bị nhiễu và nhiễu. Do đó, bạn cần một bộ lọc trục trặc để lọc ra tất cả các trục trặc không mong muốn và chỉ cho phép các tín hiệu hợp lệ đi qua. Ở chế độ tiêu chuẩn / nhanh, các trục trặc <= 50ns được loại bỏ. Ở chế độ tốc độ cao, các trục trặc <= 10ns được loại bỏ.

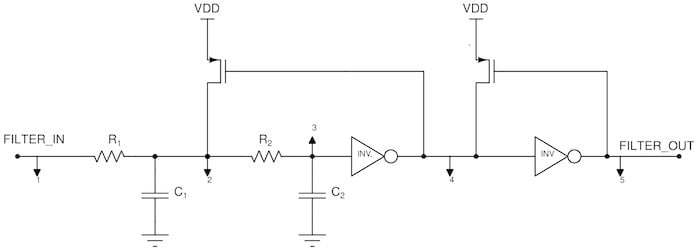

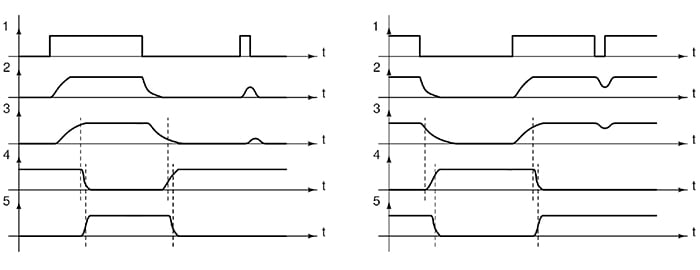

Thiết kế bộ lọc trục trặc được hiển thị trong Hình 4 và sơ đồ thời gian được hiển thị trong Hình 5.

Hình 4. Thiết kế bộ lọc trục trặc

Hình 5. Sơ đồ thời gian của bộ lọc trục trặc

Thời gian liên tục RC trì hoãn việc truyền tín hiệu và ngăn chặn bất kỳ trục trặc nào. Sự kết hợp R1, C1, R2, C2 xác định độ rộng xung của trục trặc được triệt tiêu. Theo thông số kỹ thuật I²C, bộ thu phải có khả năng triệt tiêu các xung trục trặc <= 50ns ở chế độ tiêu chuẩn và nhanh và <= 10ns ở chế độ tốc độ cao.

Tín hiệu đầu ra từ bộ lọc trục trặc được đệm và được xử lý cho các hoạt động tiếp theo bởi vi mạch.

Điện trở kéo lên trong cấu hình thoát nước mở

Bộ đệm đầu ra trên các dòng I²C ở trong cấu hình thoát mở, chúng tôi thảo luận chi tiết hơn trong bài viết của chúng tôi về phần cứng cần thiết cho bus I²C . Bất kỳ thiết bị I²C nào cũng chỉ có thể giảm tốc độ trên các dòng I²C này hoặc phân bố chúng. Để có được mức logic cao, các điện trở kéo lên được yêu cầu để kéo chúng đến đường ray điện áp trong điều kiện tam hợp.

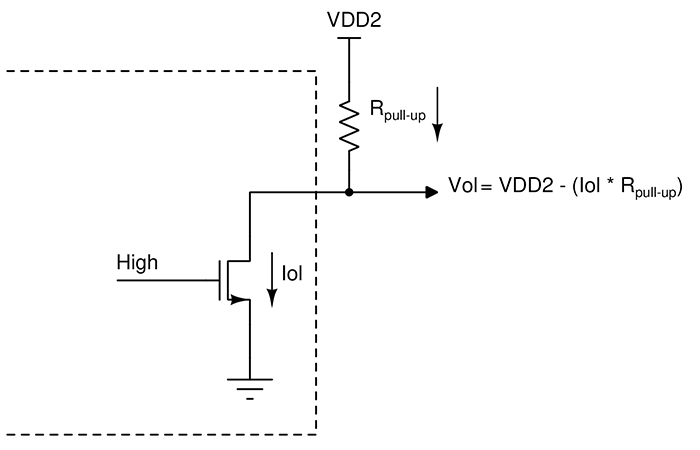

Khi thiết bị ở mức thấp, các điện trở kéo lên này hút dòng điện qua NMOS như thể hiện trong Hình 6.

Hình 6. Cấu hình cống mở

Thời gian tăng phụ thuộc vào điện trở kéo lên và thời gian điện dung ký sinh không đổi và thường dài hơn thời gian rơi vì sự rơi được điều khiển bởi thiết bị (tức là bởi NMOS). Do đó, các điện trở kéo lên khác nhau được yêu cầu cho các tốc độ hoạt động khác nhau.

Để biết thêm thông tin về điện trở kéo lên và tải điện dung, vui lòng xem bài viết của chúng tôi về toán học I²C cho điện dung và điện trở .

Không có nhận xét nào